# **Improvement of Organic Packaging Thermal Cycle Performance**

# <u>Measurement</u>

By William E. Bernier, Stephen R. Cain, Peter Slota Jr., David B. Stone\*, Christian R. LeCoz\*, Anuj Jain\*\*, Mohamed Belazzouz\*\*\* IBM Corporation, Inc. 1701 North Street Endicott, NY 13760 Phone: 607-429-3137 Fax: 607-429-3137 bernierw@us.ibm.com \*Burlington, VT \*\* Hopewell Junction, NY

\*\*\* Bromont, Quebec, Canada Glenn O. Dearing, Paul J. Hart Endicott Interconnect Technologies, Inc.

1701 North Street Endicott, NY 13760 Phone: 607-755-6435 Fax: 607-755-6969 dearing@eitny.com

# Abstract

Flip Chip Plastic Ball Grid Array (FCPBGA) modules, when subjected to extreme environmental stress testing, may often reveal mechanical and electrical failure mechanisms which may not project to the field application environment. One such test can be the Deep Thermal Cycle (DTC) environmental stress which cycles from -55°C to 125°C. This "hammer" test provides the customer with a level of security for robustness, but does not typically represent conditions which a module is likely to experience during normal handling and operation. The Flip Chip Plastic Ball Grid Array – High Performance (FCPBGA-HP) module, also known as HyperBGA<sup>TM</sup>, is one such application where a fraction of the test population may fail in DTC testing when stressed at component level. Such test failures are shown to be an artifact of the stress test itself when conditions of the test assembly are modified to better represent the application environment. DTC reliability testing has been performed on FCPBGA-HP modules as both free-standing modules as well as attached to interposers which simulate a mechanical structure more representative of a module soldered to a printed wiring board. Significant time differences in initial failures and distributions were observed along with different failure modes. The use of an interposer had a significant effect on the reliability behavior of this carrier in DTC.

#### Introduction

Standard environmental stress testing of circuit packaged semiconductor devices (modules) has evolved over time from largely ceramic based circuit packages to lower cost organic based circuit packages. Many have argued in the past that organic-based circuit packages must meet the same aggressive thermal cycle stress requirements as demonstrated on ceramic-based circuit packages. Others have argued that difficult thermal cycle stresses which provide a level of security and confidence in the use of such packaged devices by the customer do not necessarily represent conditions which will be found in many field application environments. Consequently, achievement of this level of security may come at great financial and schedule cost in order to meet unrealistic or exaggerated environmental stress conditions relative to those actually encountered in the typical application environment.

Build up layer organic based circuit packages often have difficulty achieving successful completion of -55°C to 125°C thermal cycle environmental stressing for 1000 cycles after JEDEC MSL conditioning [1, 2]. Many times the failure modes which do occur in such modules are not representative of events that may occur in routine field operational environment. In some regards this may be due to the manner of testing of the module in a socket mounted on a board. Testing in this fashion can be performed for a variety of reasons such as reuse of the test socket card in order to reduce the expense of individual cards for each tested module and savings in environmental chamber space for modules relative to typically larger cards with connectors for electrical read out. However the influence of the solder joint attachment of the module to the board can be lost when module socketing is employed only for test readings because in many cases this may have a beneficial effect of minimizing the various flexing, bending and twisting effects which may occur with an unconnected, free-standing module in the test chamber. However, performing standard board assembly of the module to the test card can often result in equally misleading conclusions since the test boards may not be built to withstand the harsh thermal cycle conditions of the -55°C to 125°C environmental stress test and have frequently resulted in board failures which can be laborious to verify and are an artifact of the test protocol. One less pleasing solution is to perform thermal cycle testing at -40°C to 125°C to avoid the artificial failures but this may not be satisfying to some application requirements. [3-7] A simple

Figure 1. This is an image of a FCPBGA-HP module without lid from top view and bottom view.

solution is demonstrated here which combines the simplicity and cost of the socket test with the field applicability of the module soldered to a test board resulting in an improved environmental stress test. This stress test may have greater applicability to the field environmental conditions while eliminating failure mechanisms which are irrelevant to the field environment. An image of the FCPBGA-HP module without lid is shown in both top and bottom views in Figure 1. A cross-sectional diagram of the FCPBGA-HP module is shown in Figure 2. There is adhesive used in the HyperBGA<sup>TM</sup> carrier construction to bond the stiffener to the build up circuitry. There is also

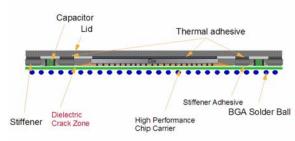

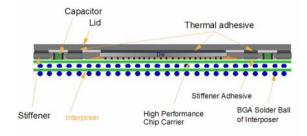

# Figure 2. This is a cross-sectional diagram of the FCPBGA-HP module (not to scale).

underfill adhesive applied as part of chip assembly processing. It may be noted from this diagram that there is a space between the underfill adhesive fillet and the adhesive fillet for the stiffener labeled Dielectric Crack Zone. This area under module level testing conditions has been identified as sensitive to environmental stressing conditions of thermal cycling and at times will demonstrate a crack forming after 500 to 750 cycles of -55°C to 125°C thermal cycling with PbSn eutectic BGA solder or as early as 500 cycles with Pb-Free Sn3.0Ag0.5Cu BGA solder

# Table 1

These are the results of thermal cycling free standing FCPBGA-HP modules with thermal cycle conditions of -55°C to +125°C and the module test vehicle description of a 52.5 mm body size test vehicle with an 18.2 mm square chip.

| Description            | MSL/Reflow<br>Condition | Sample<br>Size | Results                                                       |

|------------------------|-------------------------|----------------|---------------------------------------------------------------|

| CuOSP /<br>SAC solder  | Level 4 / 260°C         | 10             | 1 <sup>st</sup> fail: 500<br>cycles (solder<br>mask cracking) |

| CuOSP /<br>SAC solder  | Level 3 / 260°C         | 10             | 1 <sup>st</sup> fail: 500<br>cycles (solder<br>mask cracking) |

| CuOSP /<br>PbSn solder | Level 3 / 225°C         | 10             | 1 <sup>st</sup> fail: 500<br>cycles (solder<br>mask cracking) |

| ENiG /<br>PbSn solder  | Level 3 / 225°C         | 10             | 1 <sup>st</sup> fail: 750<br>cycles (solder<br>mask cracking) |

| ENiG /<br>SAC solder   | Level 3 / 260°C         | 10             | 1 <sup>st</sup> fail: 500<br>cycles (solder<br>mask cracking) |

subsequently referred to as SAC BGA solder. Data from preliminary testing is shown in the Table 1.

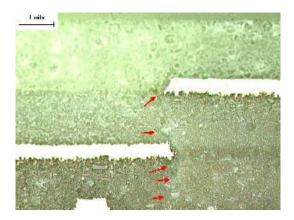

The cracking in the gap between the stiffener adhesive fillet and the chip underfill adhesive fillet is a routine occurrence with module level DTC testing. Figure 3 depicts an image in which dielectric cracking in the carrier occurs as a result of the thermal cycling environmental stress indicated in Table 1. Such cracks can propagate diagonally as well as vertically through dielectric, often through clearance holes in the carrier. Figure 4 shows a crosssectional image that results in the propagation of the

Figure 3. An example of crack propagation through the dielectric of a module experiencing DTC environmental stressing. The red arrows indicate the path of the crack.

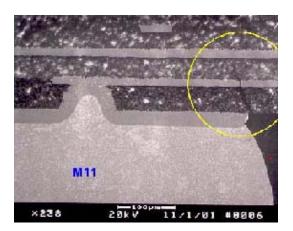

Figure 4. An example of crack propagation through the dielectric of a module and circuit line experiencing DTC environmental stressing resulting in an electrical open and test failure, highlighted in the yellow circle.

cracks formed in the dielectric which eventually sever a circuit line in the chip carrier circuitry causing an open electrical reading recorded as a test failure in the BSM (Bottom Side Metallurgy) which is circled in yellow.

#### **Experimental Description**

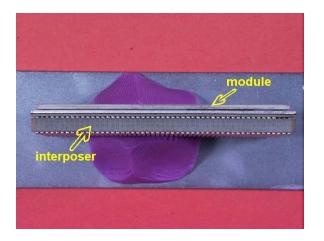

It was determined that, as part of qualification testing, environmental stress testing would be performed using preconditioning at MSL 3, MSL 4, both with reflows at 260°C for Pb-Free solder and at 225°C, and exercising Deep Thermal Cycle (DTC) stressing of -55°C to -125°C on the Flip Chip Plastic Ball Grid Array High Performance (FCPBGA-HP) module containing the IBM Cu11 chip technology with low K dielectric and the EIT HyperBGA<sup>TM</sup> organic chip carrier. This module is 52.5 mm body size with 18.2 mm x 18.2 mm chip and is shown earlier in Figure 1. An interposer card was designed to the same 52.5 mm body size as the module, 2.794 mm (0.110") laminate structure thickness and BGA attachment of

Figure 5. This is a cross-sectional diagram view of the module mounted on the interposer (not to scale).

the module to the interposer with BGA array on the bottom of the interposer as an electrical pass-through of the module array. The BGA pass through design allows the same test socket to be used as with the stand alone module. A cutaway diagram of the interposer card is shown in Figure 5. The interposer has the same physical outline as the FCPBGA-HP module.

Processing of the test assembly consisted of initial preconditioning soak of the module at 30°C and 60% relative humidity, two reflow cycles of the FCPBGA-HP module at a peak temperature of 260°C, attachment of BGA balls, either SAC (Sn-Ag-Cu alloy solder) or PbSn eutectic (63/37 Sn/Pb alloy solder), to the bottom of the interposer card followed by reflow attachment of the FCPBGA-HP module to

# Table 2.

This is the process flow for module preconditioning, interposer attachment, and module environmental stress testing.

| Process Flow for FCPBGA-HP Module             |  |  |  |  |

|-----------------------------------------------|--|--|--|--|

| Preconditioning, Interposer Assembly,         |  |  |  |  |

| and Stress Testing                            |  |  |  |  |

| Module Bake 125°C for 24 hours                |  |  |  |  |

| MSL preconditioning (MSL 3 or MSL 4)          |  |  |  |  |

| 30°C / 60 % Relative Humidity                 |  |  |  |  |

| Two module level reflow cycles                |  |  |  |  |

| (Pb-Free modules 260°C peak temperature,      |  |  |  |  |

| PbSn modules 225°C peak temperature)          |  |  |  |  |

| Third reflow cycle for interposer attach (Pb- |  |  |  |  |

| Free modules 260°C peak temperature,          |  |  |  |  |

| PbSn modules 225°C peak temperature)          |  |  |  |  |

| with SAC solder balls already attached to     |  |  |  |  |

| the bottom of the interposer                  |  |  |  |  |

| Placement of Module/Interposer Assemblies     |  |  |  |  |

| in Trays in Environmental Stress Test         |  |  |  |  |

| Chambers                                      |  |  |  |  |

| Electrical Test of Module/Interposer          |  |  |  |  |

| Assemblies in Clam Shell Socket Tester        |  |  |  |  |

| Every 250 cycles                              |  |  |  |  |

|                                               |  |  |  |  |

the top of the interposer card representing the third reflow pass of the preconditioning. Table 2 lists the process flow for the preconditioning, interposer assembly to the modules, and environmental stress testing of the FCPBGA-HP module / interposer assembly. A picture of the completed test assembly

Figure 6. This is a picture of the 52.5mm FCPBGA-HP module / interposer assembly test vehicle.

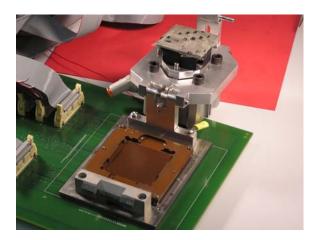

Figure 7. This is a picture of the open clam shell socket test fixture.

Figure 8. This is a picture of the 52.5 mm FCPBGA-HP module / interposer assembly test vehicle in the open clam shell socket test fixture.

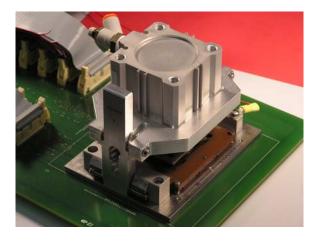

of the FCPBGA-HP module on the interposer card is shown in Figure 6. The modules on interposers were then placed in JEDEC standard high temperature plastic trays and cycled in a dual zone thermal cycle chamber at -55°C to 125°C. The module assembly was removed every 250 cycles and electrically tested for continuity in a clam shell socket test fixture shown open without the module / interposer assembly test vehicle in Figure 7, open with the module / interposer assembly test vehicle in Figure 8, and closed with the module / interposer assembly test vehicle inside it in Figure 9. The composite height of the combined module and interposer was

#### Figure 9. This is a picture of the 52.5 mm FCPBGA-HP module / interposer assembly test vehicle in the closed clam shell Socket test fixture.

accommodated conveniently within the mechanical tolerances of the clam shell fixture either with or without the interposer. The same clam shell fixture was used for electrically testing either the module alone or as assembled to the interposer.

# **Results and Discussion**

Accelerated Thermal Cycle environmental stress test with temperature extremes of 0°C to 100°C is considered to be more representative of field environmental application conditions for the FCPBGA-HP modules assembled to cards or boards Table 3 shows representative data collected in Accelerated Thermal Cycle (ATC) Testing indicating no failures occurring through 3100 cycles due to solder mask cracking and line fatigue failure (the duration of the stress testing).

FCPBGA-HP modules without interposer cards attached were tested in -55°C to 125°C DTC in parallel with modules attached to interposer cards.

At 500 cycles of DTC environmental stressing had initial failures starting at 500 cycles for the FCPBGA-HP modules without interposer cards and were found to have the characteristic opens in tested electrical nets consistent with historical mechanical fatigue found only as an artifact in this test and never found in the ATC testing on test cards. Pictures of this failure mode are shown in Figures 3 and 4. In the area of the carrier between the end of the underfill fillet for the chip and the start of the adhesive fillet for the stiffener attachment there is a crack evident in the carrier laminate structure which has caused the

#### Table 3.

These are results of thermal cycling of FCPBGA-HP module on test boards. Thermal cycle conditions: 0 to 100°C. Module test vehicle description: 52.5 mm TV on standard test cards.

| BGA<br>Description     | MSL/Reflow<br>Condition | Sample<br>Size | Results                                   |

|------------------------|-------------------------|----------------|-------------------------------------------|

| CuOSP /<br>SAC solder  | Level 4 /<br>260°C      | 10             | No<br>laminate<br>failure:<br>3100 cycles |

| CuOSP /<br>SAC solder  | Level 3 /<br>260°C      | 10             | No<br>laminate<br>failure:<br>3100 cycles |

| CuOSP /<br>PbSn solder | Level 3 /<br>225°C      | 10             | No<br>laminate<br>failure:<br>3100 cycles |

| ENiG /<br>PbSn solder  | Level 3 /<br>225°C      | 10             | No<br>laminate<br>failure:<br>3100 cycles |

| ENiG /<br>SAC solder   | Level 3 /<br>260°C      | 10             | No<br>laminate<br>failure:<br>3100 cycles |

electrical open. It is apparent that this cracking is due to the lack of mechanical support in this area relative to the adjacent areas of the module assembly. Visual inspection and electrical continuity read out of the FCPBGA-HP modules attached to interposer cards showed no such failures at the same 500 cycle check point. DTC electrical readings at 750 cycles and 1000 cycles for the FCPBGA-HP modules without interposer cards attached continued to show additional failures. The FCPBGA-HP modules attached to interposer cards continued to show no electrical failures for this mechanism at 750 cycles, 1000 cycles, or at intervals of reading every 250 cycles out to 4000 cycles at which point testing was halted.

As a result of this test it was determined that the

interposer provides additional mechanical support to the module in the area of the carrier between the end of the underfill fillet for the chip and the start of the adhesive fillet for the stiffener attachment. This support is representative of the typical application environment in which the FCPBGA-HP module would normally be used – assembled to a card or board. The fact that the failure mode completely disappeared out to 4000 cycles of one of the more challenging environment thermal cycle stress tests is remarkable. It also provides additional convincing evidence of the overall durability of the FCPBGA-HP

#### Table 4.

These are results of thermal cycle testing of FCPBGA-HP module / interposer assemblies with thermal cycle conditions: -55°C to 100°C and the module test vehicle description of 52.5 mm TV on interposer or without interposer where noted.

| Module<br>Quantity | BGA Solder | MSL/Peak<br>Reflow<br>Temperature | First Failure<br>Results for<br>Laminate in<br>DTC Cycles |

|--------------------|------------|-----------------------------------|-----------------------------------------------------------|

| 11                 | SAC        | MSL 4 /<br>260°C                  | 4000 +<br>with<br>interposer                              |

| 6                  | SAC        | MSL 3 /<br>260°C                  | 4000 +<br>with<br>interposer                              |

| 2                  | SnPb       | MSL 4 /<br>225°C                  | 4000 +<br>with<br>interposer                              |

| Control            | SAC        | MSL 4 /<br>260°C                  | 500<br>without<br>interposer                              |

| Control            | SAC        | MSL 3 /<br>260°C                  | 500<br>without<br>interposer                              |

| Control            | SnPb       | MSL 3 /<br>225°C                  | 750<br>without<br>interposer                              |

module without any footnotes or explanation of failure artifacts. Mechanical finite element modeling performed separately confirmed this mechanism. [8] In addition, line Moire' analysis of the free module also indicates the bending modes above and below the plane of the module as the temperature varies from -55°C to 125°C implying that there is considerable strain occurring to thinner, less supported areas of the module construction such as that between the chip underfill adhesive fillet and the stiffener adhesive fillet. [9]

#### Conclusions

A significant discrepancy in the data generated for evaluation and qualification of the FCPBGA-HP module versus the card or board assembled results has been shown to be an artifact of the testing modes between module level test in DTC environmental stress testing and modules assembled to cards as evaluated in ATC environmental stress testing. By introducing a durable interposer representing a board attached structure with the same physical outline as the module, the induced failure mechanism has been shown to be eliminated. At the same time the lower cost clam shell test fixture could still be used for reduction in stress testing and qualification expenses. Furthermore, FCPBGA-HP module robustness has been demonstrated to be able to be extended to a new thermal cycling environmental stress test range at a new large body size and chip size of 52.5 mm and 18.2 mm square, respectively. This technique may also be extendable to other FCPBGA module types which may not only have difficulty achieving successful results at this 180°C or alternate temperature delta, but also would represent a stress environment more typical of that experienced in most customary applications.

#### References

- 1. JESD22-A113, "Preconditioning of Nonhermetic Surface Mount Devices Prior to Reliability Testing".

- 2. JESD22-A104, "Temperature Cycling".

- Kim Blackwell, Thomas Kindl, Hal Lasky, and Ty Youngs, Qualification Results of HyperBGA, IBM's High Performance Flip Chip Organic BGA", Proceedings of the 3<sup>rd</sup> Annual Semiconductor Packaging Symposium, SEMICON West 2000, San Jose, California, July 12, 2000

- David Alcoe, "HyperBGA<sup>TM</sup>: a High Performance, Low Stress, Laminate Ball Grid Array Flip Chip Carrier", Future Fab International, Vol.10, 25 pages, July, 2001.

- 5. Jie Xue, Ken Hubbard, Phillip Li, Jennifer Tang, Jimmy Poon, Mark Brillhart, Dave Alcoe, Robert Kunz, and David Mendez, "Evaluation of Manufacturing Assembly Process Impact on Long Term Reliability of a High Performance ASIC Using Flip Chip HyperBGA<sup>TM</sup> Package", Proceedings of the 2003 Electronic Components and Technology Conference (ECTC), New Orleans, Louisiana, May 28-31, pp. 359-364, 2003.

- D. J. Alcoe, K. Blackwell, and E. Laine, "Flip Chip Packaging Reliability Advances", Advanced Packaging, Vol. 9, Issue 6, June, 2000.

- P. A. Gruber, D. Y. Shih, L. Belanger, G Brouillette, D. Danovitch, V. Oberson, M. Turgeon, and H. Kimura, "Injection Molded

Solder Technology for Pb-Free Wafer Bumping", Proceedings of the 2004 Electronic Components and Technology Conference (ECTC), Las Vegas, Nevada, June 1-4, p. 650, 2004.

- 8. D. Questad, private communications.

- D. J. Alcoe, M. A. Jimarez, G. W. Jones, T. E. Kindl, J. S. Kresge, J. P. Libous, and R. J. Stutzman, "HyperBGA<sup>TM</sup>: a High Performance, Low Stress, Laminate Ball Grid Array Flip Carrier", IBM MicroNews, Vol. 6, No. 2, pp. 26-36, Second Quarter 2000.

HyperBGA<sup>TM</sup> is a trade mark of Endicott Interconnect Technologies, Inc.