## Void Detection in Large Solder Joints of Integrated Power Electronics

Patrick Schuchardt Goepel electronics LLC

# APEX 2012 CAN TO CIS C3

## What are power electronics

- Solid-state electronic devices which control and convert electric power

- Engine control units, AC/DC-, DC/DC-converter

## What are integrated power electronics

- Advanced packages of power electronics to improve efficiency and reduce size and costs

- Based on MOSFET or IGBT technology

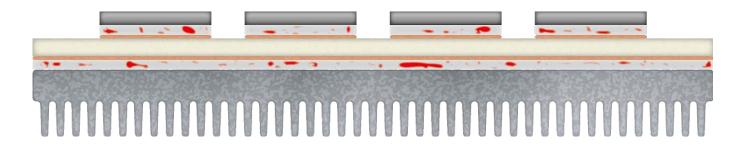

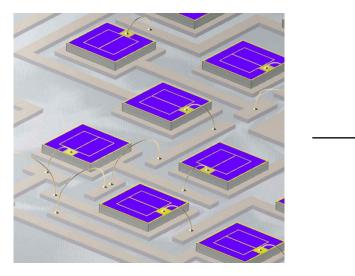

Classic 2D-wire-bond design

**IPEM**s – Integrated power electronic modules

## Integrated power electronics – Applications

- Electric vehicles, hybrid vehicles, battery charger

- Uninterrupted power supplies, emergency generators

- Converters for photovoltaic and wind power stations

- Railway drives, lighting control devices

TPS

PO" 2012

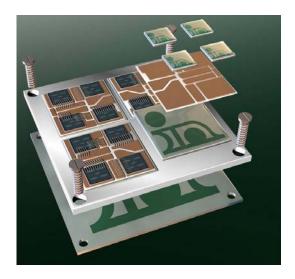

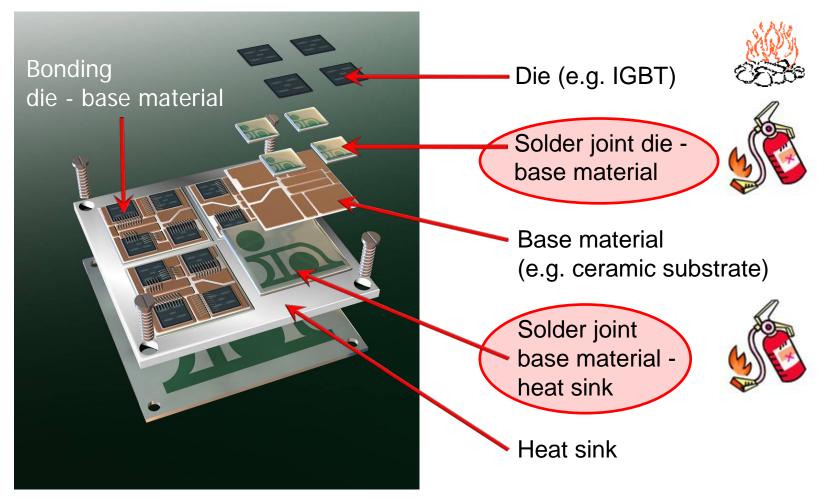

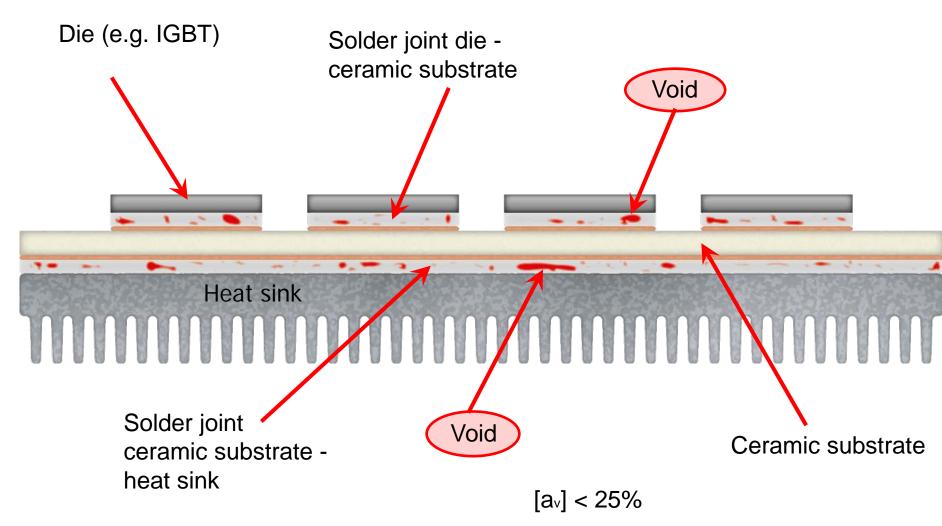

### Structure of IPEMs

source: Indium Corporation

## Structure of IPEMs

## Types of voids (source: Intel, 2005)

Tp\$ ()

APEX EXPO 2012 CAN

| Type of<br>Voids      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     | Photos |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Macro Voids           | Voids generated by the evolution of volatile ingredients of the fluxes<br>within the solder paste; typically 4 to 12 mils (100 to 300 µm) in<br>diameter, these are usually found anywhere in the solder joint; IPC's<br>25% max area spec requirement is targeted toward process voids; NOT<br>unique to LF solder joints. Sometimes referred to as "Process" voids                                                                            |        |

| Planar<br>Micro Voids | Voids smaller than 1 mil (25 µm) in diameter, generally found at the<br>solder to land interfaces in one plane; though recent occurrence on<br>Immersion Silver surface finish has been highlighted these voids are also<br>seen on ENIG and OSP surface finishes; cause is believed to be due to<br>anomalies in the surface finish application process but root cause has not<br>been unequivocally determined. Also called "champagne" voids |        |

| Shrinkage<br>Voids    | Though not technically voids, these are linear cracks, with rough,<br>'dendritic' edges emanating from the surface of the solder joints; caused<br>by the solidification sequence of SAC solders and hence, unique to LF<br>solder joints; also called sink holes and hot tears                                                                                                                                                                 |        |

| Micro-Via<br>Voids    | 4 mil (100 μm) and more in diameter caused by microvias in lands; these voids are excluded from 25% by area IPC spec; NOT unique to LF solder joints                                                                                                                                                                                                                                                                                            |        |

| Pinhole<br>Voids      | Micron sized voids located in the copper of PCB lands but also visible<br>through the surface finish; Generated by excursions in the copper<br>plating process at the board suppliers                                                                                                                                                                                                                                                           |        |

| Kirkendall<br>Voids   | Sub-micron voids located between the IMC and the Copper Land;<br>Growth occurs at High Temperatures; Caused by Difference in Inter-<br>diffusion rate between Cu and Sn. Also Known as "Horsting" Voids.                                                                                                                                                                                                                                        |        |

Communities U

## Test Equipment Requirements

TPS

PO" 2012

- Reconstruction of overlaying solder joints

- Separation of voids in different layers

- Determination of relevant parameters for every layer:

- Biggest void, Sum of all voids

- Local distribution of voids = thermal connection

- Measurement accuracy: 0.1mm<sup>2</sup> 0.3mm<sup>2</sup>

- Complete inspection within the production cycle

- Inspection in (partly-) mounted state, e.g. with heat sink

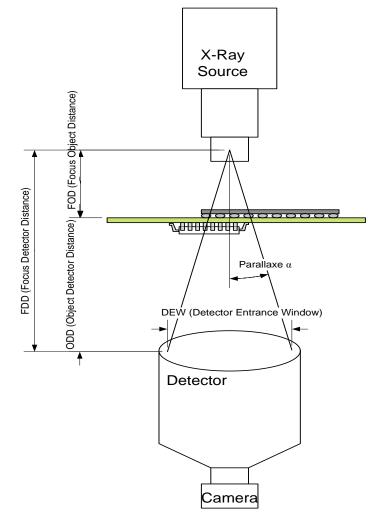

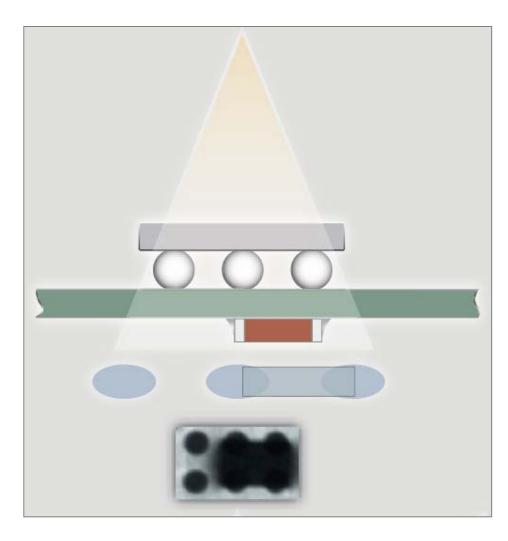

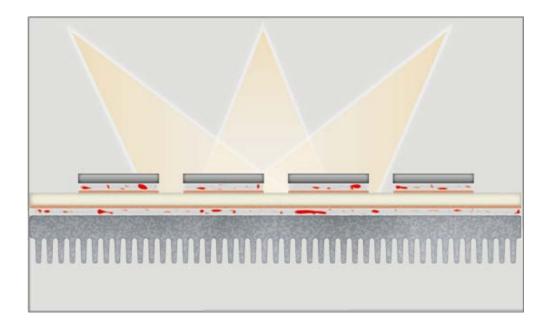

## **XRay Inspection Basics - Review**

TPS

CAN

XRay Beam penetrates the pcb -Dense material – high absorption -Less signal on the detector

SCI INTERNATION

Geometry defines -Magnification -Parallax angle

APEX EXPO" 2012

IPC

#### **Def: Automated Optical Inspection**

Main

**Principle**

2D / 2.5D / 3D

One or more images of the Area of interest

simple or one-layer analysis or multi-layer analysis with 3D image

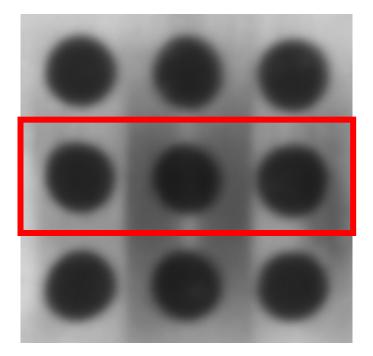

## 2D X-ray Technology: Basic Principle

PCB is always radiated orthogonally!

## 2D X-ray Technology: Pros and Cons

### Pros

TPS

- Cost-effective system architecture

- High speed testing

PO" 2012 CAN

Simple programming

Overlayed components and solder joints (e.g. at double-sided assembly) can't be inspected

## Test of integrated power electronics

- Test of <u>one</u> solder layer (die ceramic substrate) possible after first solder process, <u>but:</u>

- No separation of overlaid (second) solder joint possible !

## APEX OF 2012 ONLY TO CIS

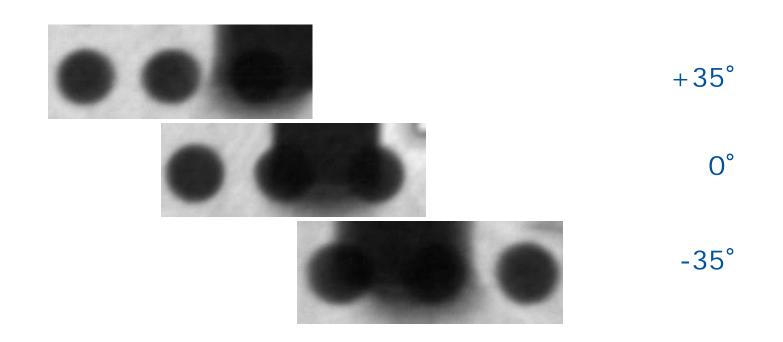

## 2.5D X-ray Inspection: Basic Principle

Hidden solder joints are "separated" by off-axis view.

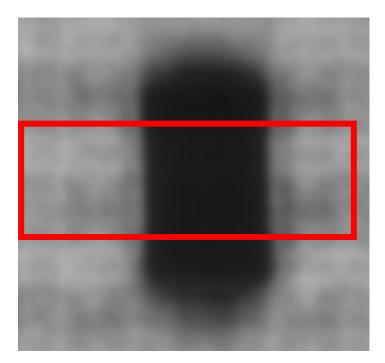

## APEX EXPO 2012 CAN 2D / 2.5D X-ray technology:

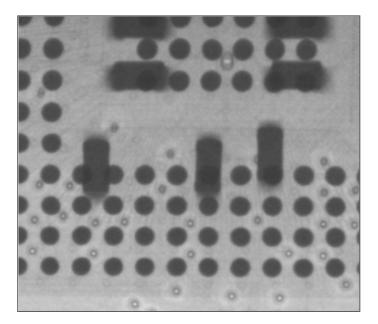

## **Inspection of integrated Power Electronics**

TPS

Inhomogeneity by heat sink, ceramic substrate and die

Voids can't be assigned to a certain layer

## 2.5D X-ray Inspection: Pros and Cons

## Pros

PO" 2012 CAN

Overlayed components (e.g. at double-sided assembly) possibly testable

TPS

- Very high programming effort

- Consistent library not usable

- High testing times

## Test of integrated power electronics

- Test of <u>one</u> solder layer (die ceramic substrate) possible after first solder process, <u>but</u> changes after the second solder process likely!

- Separation of overlaid solder layers impossible (random positions of voids)

## APEX EXPO 2012 CANING TOP COLORING COLORING

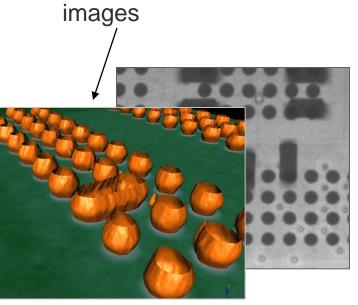

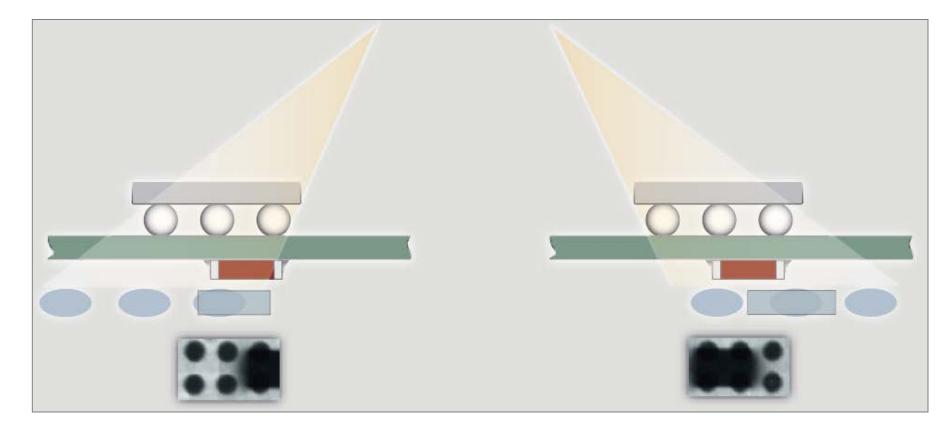

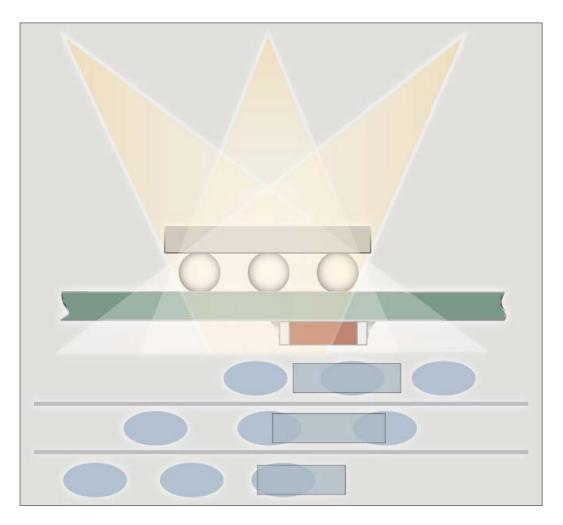

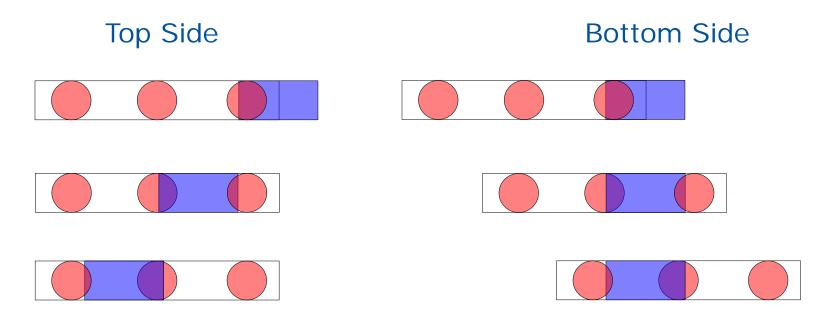

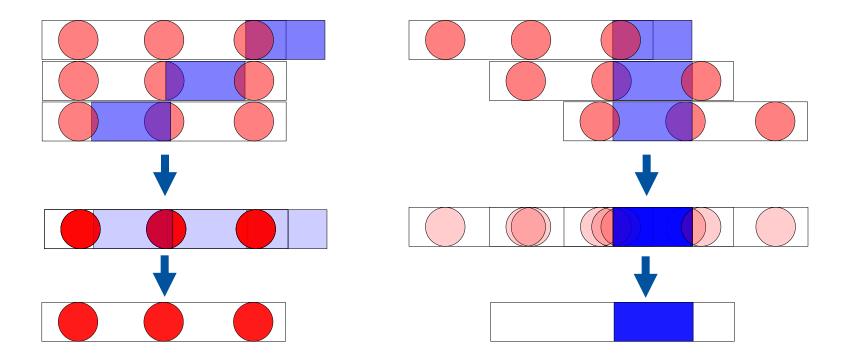

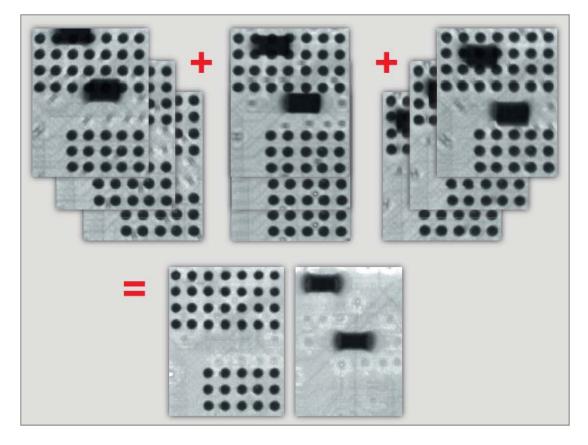

## 3D X-ray Technology: Basic Principle

PCB is radiated fromdifferent angles.Image basis results fromseveral 2D projections.

#### Multiple projections from several angles

Simultaneous reconstruction of top and bottom side

#### Reconstruction of individual slices (i.e. PCB Sides)

#### Simultaneous reconstruction of top and bottom side

#### Reconstruction of individual slices (i.e. PCB Sides)

## APEX EXPO 2012 CANT TO CIS C3

## 3D X-ray Technology: Opportunities

Algorithmic reconstruction of any layers.

Inspection of double-sided assembled PCBs.

## 3D X-ray Technology: Pros and Cons

TPS

### Pros

(PO" 2012 ON

Cons

- Safe inspection of overlaid components and solder joints

- Inspection of single layers for improved results

- Reconstruction enables a safe and convenient fault analyses

- Simple test program generation by consistent library

• Higher initial price

# APEX 2012 CANT TO CIS C3

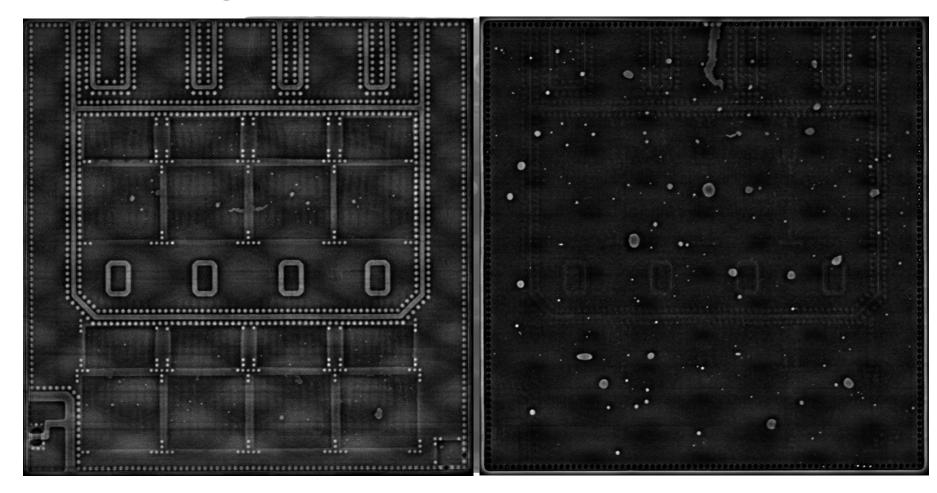

## 3D X-ray technology: IPEMs

- Inspecting the assembled IPEM –through heat-sink and housing

- Separating the area of interest in several vertical layers

- Analysis of voids number, distribution, dimensions...

## 3D X-ray Technology with adapted Image Capturing and Reconstruction

Tp>

14 February 2012 14 Echrugery 2012

APEX EXPO 2012 CAN

IPC

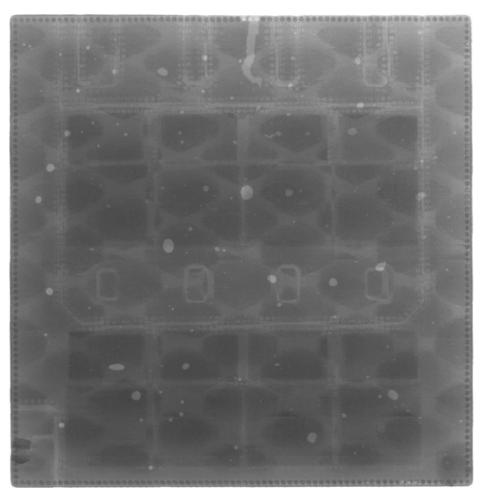

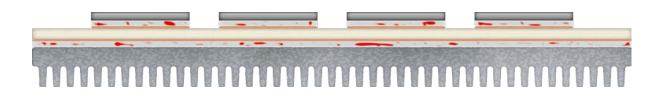

## Application example

TPS

PCB size

SI05 "O

- Assembling top side:

- Solder joints top side:

- Assembling bottom side:

- Solder joints bottom side:

- Resolution:

220mm x 90mm

24 IGBTs, 24 diodes

48 /  $\sum 37$  cm<sup>2</sup>

- heat sink

- 3 / ∑ 108cm<sup>2</sup>

- 11µm / Pixel

• Cycle time (double-sided inspection): 47s

## **Experiences and Limitations**

TP>

#### Experiences

PO" 2012 CA

- Soldering process based on printed solder paste

- Heat sink made of AISiC (Aluminium Silicon Carbide)

- High inspection quality and measurement accuracy possible

#### Limitations / Challenges

- · Heat sink made of copper or stainless steel

- Soldering process effects very thin voids (reduced detectability)

- System modification (x-ray tube, intensifier) is needed

## ed

## Summary

- Inspection of integrated power electronics = sophisticated test task

- X-ray inspection based on 2D / 2.5D principles not utilisable

- Full 3D inspection with adapted image capturing and reconstruction is necessary for test task