### A High Performance and Cost Effective Molded Array Package Substrate

Philip Rogren\*, Pierangelo Magni, Maura Mazzola, Mark Shaw, Giovanni Graziosi, Claudio Maria Villa \*EoPlex Technologies, 3698-A Haven Avenue, Redwood City, CA 94063 ST Microelectronics, Via C. Olivetti 2, 20041 Agrate Brianza, Italy

#### Introduction

In this article we present both a relatively new and innovative family of packages that is suitable for medium pin count needs and an innovative method for fabricating the substrates for such a package. With respect to lead count, this packaging family is positioned between BGAs and "standard" QFN with single rows of pads. The package is characterized by the extreme design flexibility in terms of I/O count, location and shape, allowing a wide range of customization only limited by PCB layout constraints. Its structure looks like a metal QFN but the pad-out is more similar to LGA. This package family is characterized by multi-row designs with the possibility to have exposed partial/full ground and/or power rings. All this allows a relatively large footprint reduction compared with the same I/O counts in a TOFP package, and a significant reduction in total package height. Simplified assembly flow and easy handling leads to a package with total cost that is competitive to BGAs and TOFPs, while also allowing testing on strip.

The existing substrate fabrication techniques are shown for this package along with a new and potentially low cost sacrificial print-forming technique.

#### **QFN-MR** Package

QFN Multi Row (QFN-MR) is a package family that targets all of the above characteristics, including simplified assembly and test. It shares the staggered and multi-row QFN outlines (JEDEC MO247) (see Figure 1), but is differentiated from them by the absence of metal connectors holding each package element in its proper position. To accomplish this, the manufacturing methods for the substrate are also substantially different.

Figure 1: QFN-MR 7x7x0.7 mm 88 I/O

While staggered QFN leadframes look like the ones in Figure 2 with all feature pads connected to the main frame, QFN-MR at the end of assembly and before final separation, presents all pads electrically isolated with the packages still remaining on the original metallic frame. This allows a "strip testing" option with multiple packages contacted at the same time (parallel testing) and extremely easy handling of parts.

Separation of units from the leadframe is done using a sawing process. Since only mold compound is cut, sawing is a much faster and cleaner operation than with leadframe based QFNs.

Figure 2: Standard Multi-Row QFN Leadframe

Figure 3 is a strip with a blow-up of an individual package, showing all pads separated and ready for strip wise testing. This option is extremely useful for ultra small packages where single device handling is extremely critical. Sawing and testing can be done on metal frames with sticky tape. Final sorting and finishing are done on pick and place machines that use basic die attach concepts.

Size, location and shape of the pads can be designed in virtually infinite combinations, including varying the pitch of some pad rows to facilitate the inner row routing on the final application board. Ground ring, power rings or multiple pad connections are also feasible, as shown in Figure 1.

Figure 3: Molded isolated strip

In terms of package size, only BGAs can have a better ratio of die/package outline, and then only if the full area of the BGA can be used to distribute the ball array.

#### **Electrical Performance**

Analyzing the QFN-MR structure, the package electrical parameters are mainly depending on bond wire contribution. Thanks to the high level of miniaturization and short electrical paths, the RLC parasitic values show better electrical performance versus other leadframe package families comparable with QFN-MR with respect to the number of leads and cost.

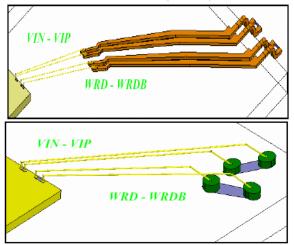

The comparison was made with an S parameters extraction using the full wave approach (no frequency limitations) for which the electromagnetic radiation is taken into account. Two differential pairs located on package corner areas (worst case because of longer paths) have been simulated in order to compare the insertion loss from 1GHz to 8GHz.

Figure 4: 3D models; designs not to scale

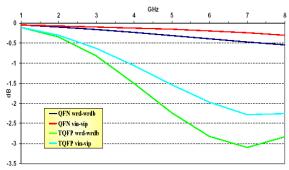

Figure 5: QFN-MR vs. QFP insertion loss

Assuming -1db as acceptable loss, the QFN-MR working range extends to more than 8GHz, which is much better than QFP for which the working range is to only 3-4GHz.

#### **Thermal Performance**

Thermal dissipation capability of the QFN-MR package with exposed pad structure is one of the key features that make it an attractive alternative to BGAs. Compared to standard exposed pad packages, QFN-MRs have much higher I/O density and comparable thermal resistance making QFN-MR compatible with most medium power applications in consumer electronics.

### Figure 6: BGAs vs. QFN-MR Theta J-A on 2s2p PCB

If we compare the most common exposed pad packages, assuming the same die size and the components mounted on the same system, we can easily evaluate the impact of the exposed pad thickness on Theta J-A. Typical pad thicknesses range from 60  $\mu$ m for QFN-MR to 200  $\mu$ m for QFNs. The thermal resistance variation within that range is some 5 %.

|                  | E-Pad<br>(mm3) | PCB footprint<br>(mm2) | Theta j-a<br>(°C/W) |

|------------------|----------------|------------------------|---------------------|

| TQFP 7x7 e-pad   | 4x4x0.125      | 9x9                    | 20.2                |

| TQFP 10x10 e-pad | 4.5x4.5x0.125  | 12x12                  | 19.7                |

| TQFP 10x10 slug  | 6x6x0.5        | 12x12                  | 18.0                |

| QFN 9x9          | 4.1x4.1x0.2    | 9x9                    | 22.1                |

| QFN-MR 7x7       | 4.6x4.6x0.06   | 7x7                    | 23.2                |

Figure 7: E-Pad packages Theta J-A on hard disk drive

Finally, benchmarking all the possible exposed pad packages with similar pin counts, QFN-MR offers the best compromise in terms of miniaturization and thermal dissipation at a very competitive cost.

#### **Manufacturing Process Etched Frame**

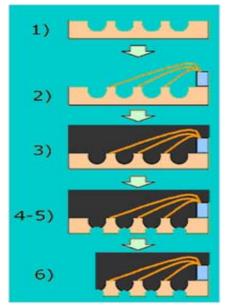

Figure 8 shows a simplified assembly flow of the double etched leadframe QFN-MR substrate:

- 1) Leadframe is received from supplier with top etching featuring the future bottom design

- 2) Standard die attach and wire bonding on rigid substrate.

- 3) Standard molding (map type)

- 4) Back-etching of the excess of metal uncovered by plating

- 5) Possible strip testing

- 6) Separation by sawing

Figure 8: Assembly flow

The only draw-back of QFNs, relative to BGAs and QFPs is that wire bonds must extend from the die to the position of their second level I/O, sometimes far away from the pads on the die. This disadvantage, as we will see, is actually an advantage for the electrical performances.

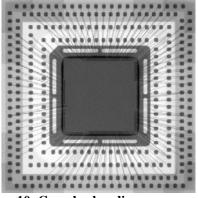

Complex bonding can be overcome by specific molding processes like "compression molding". In Figure 10, a QFN-MR 13x13 with 312 I/O with 394 Au wires of 0.8 mils diameter is shown by X-ray. Molding was done with "compression" technology that completely avoids resin flow in the mold cavity, allowing an extreme reduction in wire sweep (less than 1.5%) even on long (4.9 mm), thin (20 microns) wires.

Figure 10: Complex bonding

#### Lead Frame Design Electroplated Frame

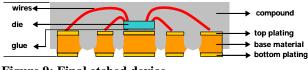

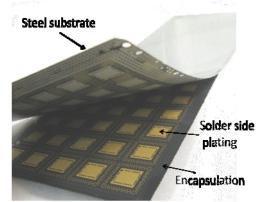

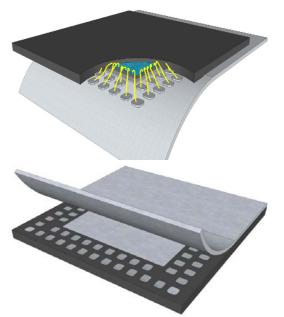

An alternative to the back etched strip is a strip with a steel base on which the die pad and wirebond pads are electroplated. The electroplating process for the pads creates a 'mushroom structure' that, after molding, anchors the metallization into the mold compound. The difference from the backetching process is that to achieve a molded strip with isolated pads, the base steel substrate is simply peeled away from the mold compound and pads.

Figure 11: Example of electroplated wirebond pads 'mushroom structure'

Figure 12: Peeling of steel substrate from molded devices

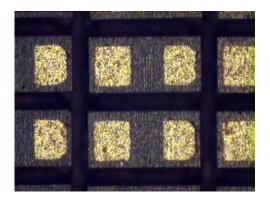

The electroplated technology also has an advantage with respect to the etched version in creating very small and thin structures. This makes the technique suitable for micro-packages that do not exceed 1 mm per side and 0.4 mm overall thickness.

Fig 13: An example showing the bottom view of 0.3mm by 0.6mm micro-packages formed using the electroplating technique after singulation

# Molded Array Package Substrate Manufactured by Print Forming

Both the double etched and plated substrates for molded array packages provide all of the advantages cited but they also present opportunities for improvement. Specifically, both approaches are still costly compared to conventional QFN lead frames and rely on the environmentally unfriendly processes of plating and etching. In response to these short comings, EoPlex Technologies has developed a substrate based on its print manufacturing technology that promises to be both environmentally friendly and less costly than the competing technologies. EoPlex's print manufacturing technology, High Volume Print Forming (HVPF<sup>TM</sup>), is based on manufacturing small complex structures by depositing successive layers of materials by printing and then converting the printed "ink" to their final properties by some sort of a heat Central to the technology is the treating step. development of fugitive materials that provide a place keeper for open space within a structure during print forming but are removed from the structure during the heat treating process. These techniques and materials are applied to create substrates that allow virtually unlimited flexibility in the design of package components.

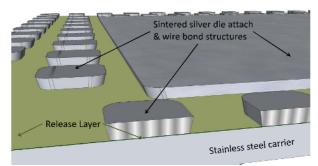

EoPlex's print-formed substrate consists of package components arrayed on a stainless steel carrier in a manner that is similar to the electroplated design. The difference is that in the print-formed version, all of the packages' pads, rings, etc., are deposited as silver paste and sintered to form solid structures suitable for gold thermo sonic wire bonding. One advantage of this process is that it is a less expensive manufacturing process. A second advantage is that it is a fully additive process and is, therefore, more environmentally friendly than plating.

The print-forming process starts with the creation of a preform on the steel carrier into which the silver paste will be deposited to precisely shape the package components.

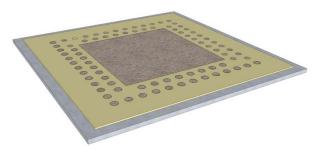

## Figure 14: Fugitive mold formed on stainless steel carrier

The preform material is a proprietary organic fugitive material that is precisely deposited by printing and then completely burned away during the sintering process. The primary purpose of the preform is to form pads with a shape that will lock the pads into the mold compound. In this case, the pads have a conical frustum shape with the wire bond surface larger than the soldering surface. Figure 14 and 15 illustrate the preform configuration.

# Figure 15: Details of the fugitive to create a shape that will be locked into the molding compound

After the preform has been created on the carrier, it is filled using printing techniques.

Figure 16: The fugitive preform is filled with silver paste specifically formulated to provide a highly bondable surface after sintering

The material that is used for this process is a special formulation of silver powders and organic vehicles that is optimized to leave a surface suitable for high yield wire bonding.

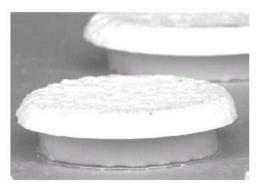

The paste is cured to provide temporary green handling strength and then the whole structure is fired in a controlled atmosphere at between 850°C and 900°C. During firing, the fugitive and vehicle materials burn away, leaving no ash, and the silver sinters to a high density metal mass.

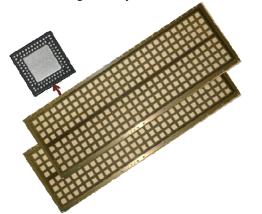

**Figure 17: Completed print formed substrates**

#### Figure 18: The steel carrier peels away easily after molding, leaving electrically isolated pads and solder pads clean and ready for soldering

Assembly flow for the print-formed substrate is very similar to that of the electro plated substrate and the steel carrier peels away easily after molding, leaving a surface that is clean and ready for soldering.

Controlling the adhesion of the pads to the carrier required the development of a release layer on the carrier. This release layer must provide adequate robustness during the assembly operation and low enough adhesion to allow for the carrier to be easily peeled away after molding. In addition, the release layer must facilitate clean separation from the silver pads without any residue that would inhibit soldering. For print formed silver, the release layer is a complex of oxides and proprietary materials that sticks tenaciously to the stainless steel while forming an adequate bond for assembly operations to the sintered silver.

Figure 19: The release layer is the key to balancing the conflicting demands of adhesion during assembly and peeling after molding

#### Conclusion

It is very desirable to develop a substrate to replace the QFN type leadframe for Molded Array Packages. A substrate provides a removable carrier for the package terminals, power and ground rings, and die pad(s), eliminating the electrical and mechanical interconnection of package components after the carrier is removed. Substrates allowing for removal of the carrier after molding by etching it away and by peeling it off have been advanced but are not ideal, being limited primarily because of cost. EoPlex Technologies has developed a substrate with a peelable carrier that is manufactured by a proprietary printing process that promises to significantly reduce substrate cost while maintaining all of the desirable features of a molded array package substrate.

#### References

Yi-Shao Lai et al "Development and performance characterizations of a QFN/HMT package", ECTC 2008. May 2008 Page(s):964 – 967

Pierangelo Magni et al "WPLGA: new package family for medium pin count with design flexibility" EMPC2009 Rimini June 2009

Charles S. Taylor, Paul Cherkas, Hilary Hampton, John J. Frantzen, Bob O. Shaw, Dr. William B. Tiffany, Dr. Leonard Nanis, Dr. Philip Booker, Amr Salahieh, Richard Hansen, "Spatial Forming" A Three Dimensional Printing Process"; 29 January – 2 Feb, 1995; IEEE Publication

US Patent number 5,348,693; Taylor et al.